Multiprocessors on FPGA4U

From Fpga4u

Contents

Description

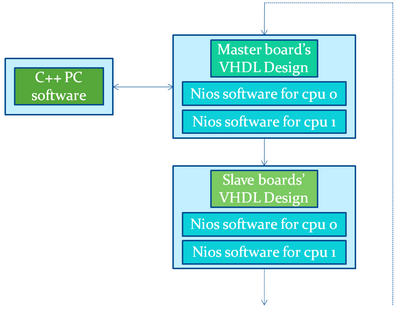

The project’s goals are to build a complete multiprocessor architecture, by building the hardware components needed, defining communication protocols, conceiving some system on programmable chip and developing software application on a computer.

The FPGA4U boards will be used to parallelize some algorithm.

Project files

Here are the developed software projects:

- Quartus 7.0 project for the main (master) board: MultiFPGA4U_master.zip

- Quartus 7.0 project for the others (slave) boards: MultiFPGA4U_slave.zip

- QDevelop C++ PC software project: MultiFPGA4U_PC_soft.zip

Documentation

Here are the project’s main report and the final presentation’s slides:

Report

Final_presentation

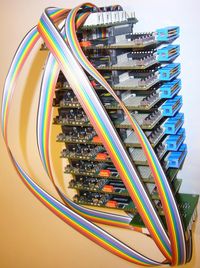

Additional hardware components needed

To be able to use the project, we need to:

- Connect the board on the bottom to the board on the top with the dedicated cable.

- Isolate boards from each other to avoid short-circuits.

Remarks about system's boot

The VHDL designs have to be put inside the EPCS flash memory of each board, since we cannot download the bitstreams with only one USB port. The USB port is used to transfer data and the Nios software codes dynamically at each execution.

If more than three boards are connected in the system, additional power supplies have to be connected (not only the USB power supply). Each power supply can power approximately three boards.

When the boards are powered, some manual reset has to be done to ensure the boards are in their initial states.

System architecture

The different parts of the system are shown here:

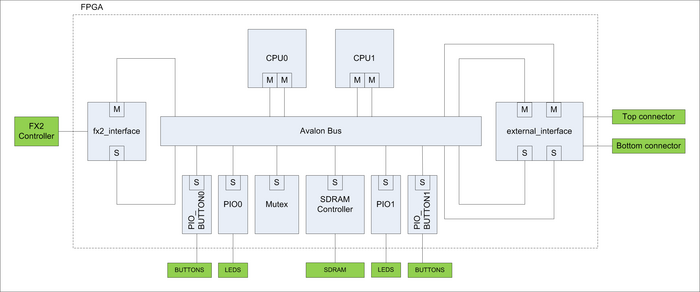

Here is the master board’s bloc diagram:

The slave boards’ designs are similar but without the fx2_interface.

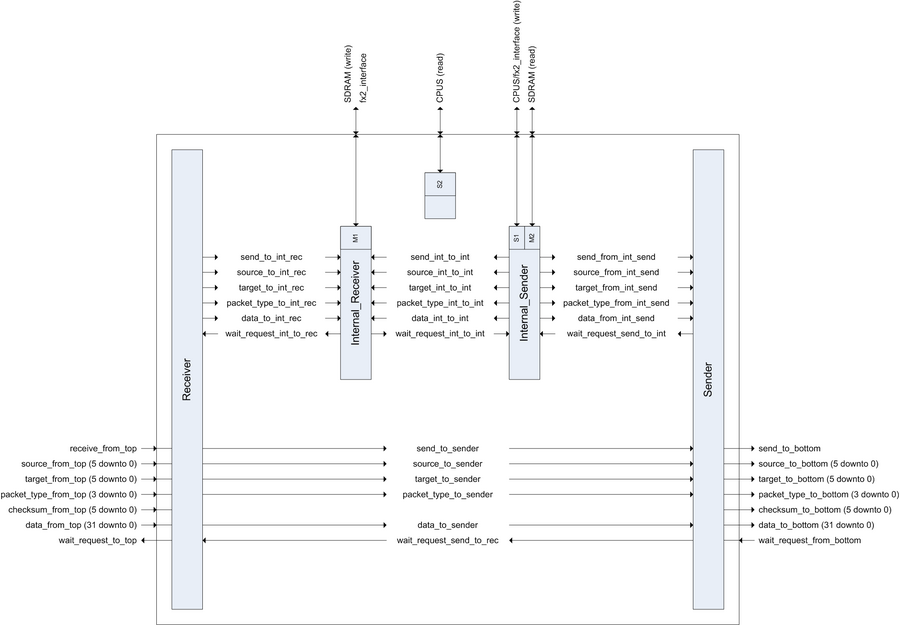

Here is the bloc diagram of the external_interface's second implementation (not included in the report):

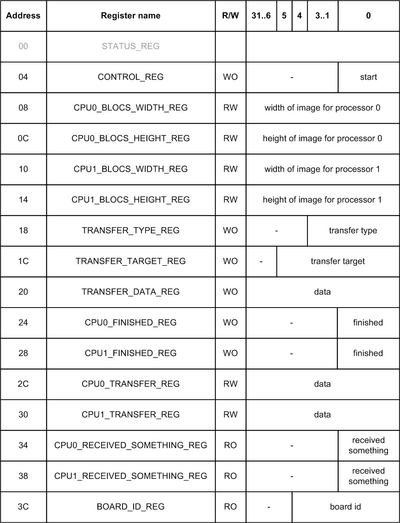

And here is the external_interface's registers:

Timing diagram

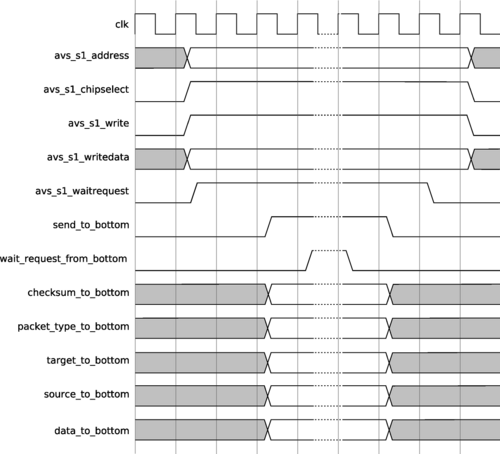

Here is some example of transfer. The fx2_interface write inside the external_interface through Avalon bus. The external_interface then forwards data to the board on its bottom :

The number of cycles between the Avalon transfer and the moment we put the send_to_bottom signal to ‘1’ is not exact on the diagram.

Nios software primitives

Here are the primitives available from the Nios processors that abstract the underlying hardware :

void leds_write(char number);

unsigned int buttons_read();

unsigned int getWidth();

unsigned int getHeight();

void finished();

unsigned int getCpuId();

void send(unsigned int target, unsigned int data);

unsigned int receive();

--Stéphane Schild 15:47, 10 February 2008 (CET)